FPGA処理をROSコンポーネント化する自動設計環境

従来のコンポーネント開発における問題

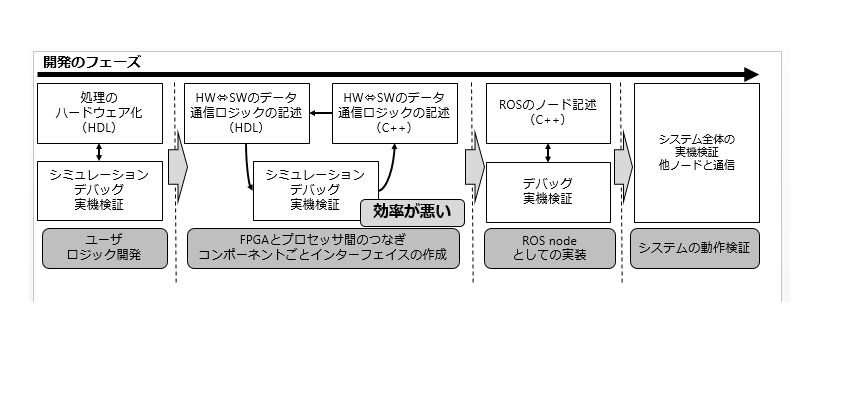

HW/SW協調設計における従来のコンポーネント開発フローを図1に示す。FPGA処理のコンポーネント化では、初めにハードウェア化する任意の処理対象を決め、ハードウェア化を行う。この際の任意の処理ハードウェアをここではユーザロジックとする。ユーザロジックへのデータ入力やデータ出力を使用する場合はプロセッサとFPGAが通信できるインターフェイスを作成する必要がある。インターフェイス作成には、FPGAにおけるデータ受け渡しのための通信路の設計、通信トランザクションの考慮、回路の実装が伴う。ソフトウェア側では、FPGA側に実装した通信路へのデータ通信の読み書きの回数やバイト数を考慮する必要がある。インターフェイスを作成し、FPGA処理のコンポーネント化が完了したあとに、ROSの通信モデルに準拠した宣言を追加することで1つのROS準拠FPGAコンポーネントが完成する。

FPGA上における開発であるため、ユーザロジックの開発にはHW/SW間の通信のためのデバッグや動作検証が伴い、回路開発のコストは大きい。そのため、ユーザロジックをシステムへの導入のためのコンポーネント化にかかる開発コストも大きく、非常に効率が悪いという問題があった。

図1:HW/SW協調設計における従来のコンポーネント開発フロー

コンポーネント自動設計環境cReCompの提案

上記において提起した問題に着目し、コンポーネント開発効率の向上のためにコンポーネント自動設計環境cReComp(creator for Reconfigurable Component)を提案する。なお、提案する設計環境はGitHubにおいてオープンソースで公開中である[1]。各コンポーネントにおいて異なる、ユーザロジックとソフトウェア/ハードウェア間通信のトランザクション(読み書きの回数、データサイズ)を定義することで、ユーザロジックに応じてFPGA処理を自動的にコンポーネント化する。

cReCompのシステム生成モデル

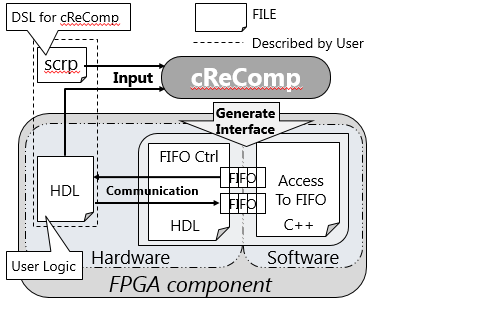

cReCompにおけるシステム生成モデルを図2に示す。cReCompにおける自動コンポーネント化ではコンポーネント化対象のユーザロジックと通信トランザクションを定義するためのScrp(Specifier for cReComp)ファイルを入力とする。開発者が記述するのはユーザロジック(HDL記述ファイル)とScrpファイルであり、コンポーネント化に必要となるソフトウェア/ハードウェア間の通信路の回路記述やソフトウェア記述は必要ない。入力ファイルに対して自動生成するのはハードウェア/ソフトウェア間通信の制御ロジックが記述されたハードウェア(HDL記述ファイル)とFIFOバッファへアクセスするためのソフトウェア(C++ファイル)の2種類である。これら2つを総称してコンポーネント化の際に生成されるインターフェイスとする。

図2: cReCompのシステム生成モデル

ARM-FPGAの通信方法

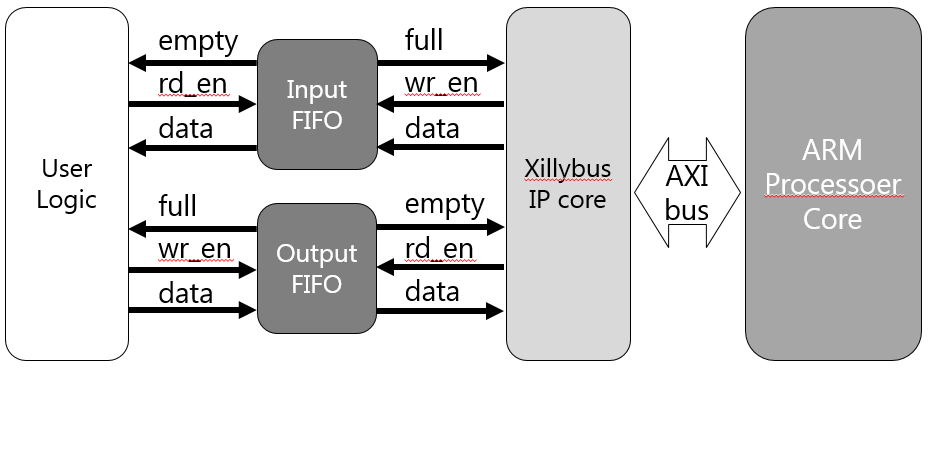

ROS準拠FPGAコンポーネントをProgrammable SoC(ARM+FPGA)上に実装するためにはFPGA上のユーザロジックに対して、プロセッサ上のソフトウェアからアクセスするための通信路が必要となる。具体的なARM-FPGAの通信方法の検討のため、Xillybus社が無償で公開しているProgrammable SoCのZynq向け開発プラットフォームであるXillinux(試用版)をしようすることとした。XillinuxはZynqのARM上において動作するLinux OS(Ubuntu)であり、FPGAとARMプロセッサ間の通信が可能なFIFOバッファに対してデバイスファイルとしてread/writeが可能である(図3)。したがって、FIFOバッファに対してユーザロジックを接続し、任意の通信を行う。FIFOバッファは32bitと8bitの2種類があり、データ転送用に32bit、デバッグ用に8bitを使用する。ROS準拠FPGAコンポーネントでは、FPGA回路へのInput/Output用の2つのFIFOバッファを32bit、8bitのそれぞれにおいて用いることで、ARMプロセッサとFPGAのそれぞれが独立に動作し、任意のタイミングでFIFOのバッファへのread/writeすることを可能とした。

図3:XillinuxにおけるSW/HW通信

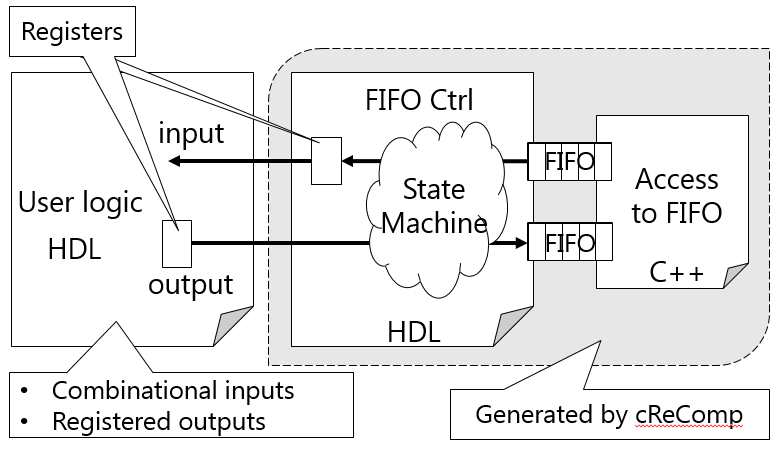

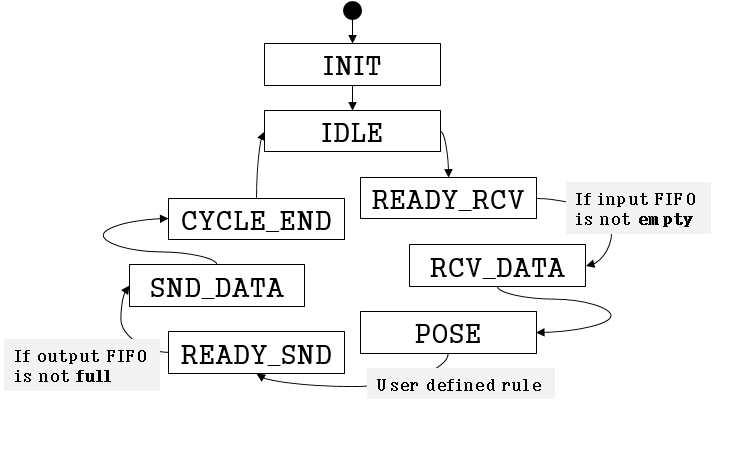

コンポーネント化対象のユーザロジックモデルとステートマシン生成

cReCompにおいてコンポーネント化の対象となるユーザロジックモデルを図4に示す。cReCompにおいてコンポーネント化の対象となるユーザロジックは入力信号は組合せ論理、出力信号はレジスタ出力であるものを対象とする。そこで、対象のユーザロジックとプロセッサがデータのやり取りを行えるようにcReCompは図5に示すステートマシンを生成する。プロセッサがユーザロジックへデータ入力をする際はREADY_RCVステートとRCV_DATAステートにおいてInput用のFIFOバッファからデータをレジスタに受け取り、ユーザロジックへデータを入力する。ユーザロジックがプロセッサへデータを出力する際は、READY_SNDステートとSND_DATAステートにおいてユーザロジックのレジスタ出力の値を直接Output用のFIFOバッファへ出力する。

対象とするユーザロジックは現時点では直接的なHDL記述によるものであるが、今後さまざまな形式に対応していく予定である。

図4:コンポーネント化対象のユーザーロジックモデル

図5:FIFOバッファ制御のためのステートマシン

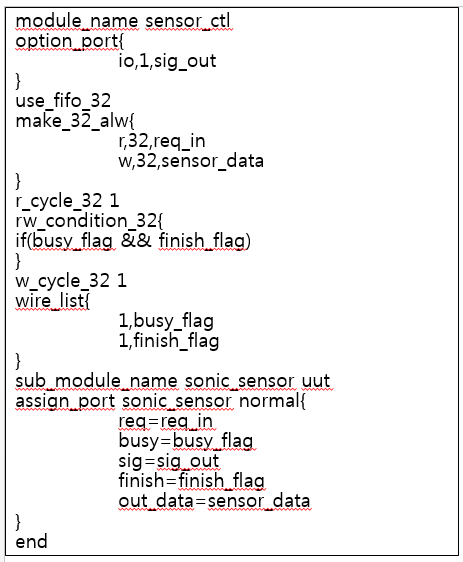

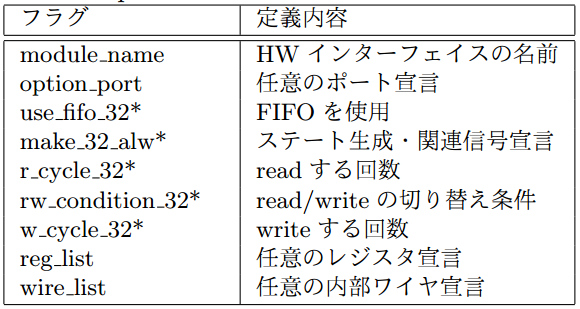

ScrpファイルによるSW/HW通信トランザクションの定義

cReCompではScrpファイルを使用して、ソフトウェアとハードウェア間の通信のトランザクションを定義する。Scrpファイルの例を図6に示す。テンプレートはcReCompを使用する際に生成することができる。各設定項目はフラグと称し、フラグに対応したそれぞれの定義を行うことによってコンポーネントの自動生成が可能である。なお、表1に示したフラグは32bit FIFO用のみのフラグであり、*が付加したフラグは8bit FIFOにも対応するフラグである。また、cReCompにおいてScrpファイルテンプレートの生成時にユーザロジックの指定を行えば、対象の回路の入出力信号がテンプレート内に自動で記述される。したがって、ソフトウェア/ハードウェア間通信用の回路のためにHDL記述をしなくても、Scrpファイル内において信号を自由に配線することが可能である。

図6:Scrpファイルの例

表1:Scrpファイルにおける各フラグの定義内容

[1]cReComp : https://github.com/kazuyamashi/cRecomp.git