BBPCプロジェクト

背景

VLIWアーキテクチャは命令レベル並列処理において、ハードウェアコストの低下や動作の高速化などの利点があり、汎用プロセッサおよび組み込み/DSP プロセッサアーキテクチャとして導入される。代表的な製品は富士通のFR-V、PixelworksのBSP15/16、STMicroelectronicsのST231など、多くのベンダーからリリースされている。また、半導体集積度の向上につれ、1つのプロセッサ上で複数のスレッドを処理するマルチコアプロセッサが登場し、実行速度の向上に注目が集まっている。

VLIWアーキテクチャって何?

VLIW (Very Long Instruction Word)アーキテクチャでは、命令長を長く取り、ロード、ストア、演算、分岐などのRISC (Reduced Instruction Set Architecture)操作を複数並べることで処理の単位となる命令語(VLIW命令) を構成する。このVLIW命令の実行により、複数のRISC操作を同時に処理する命令レベル並列処理を実現し、性能向上を図る。

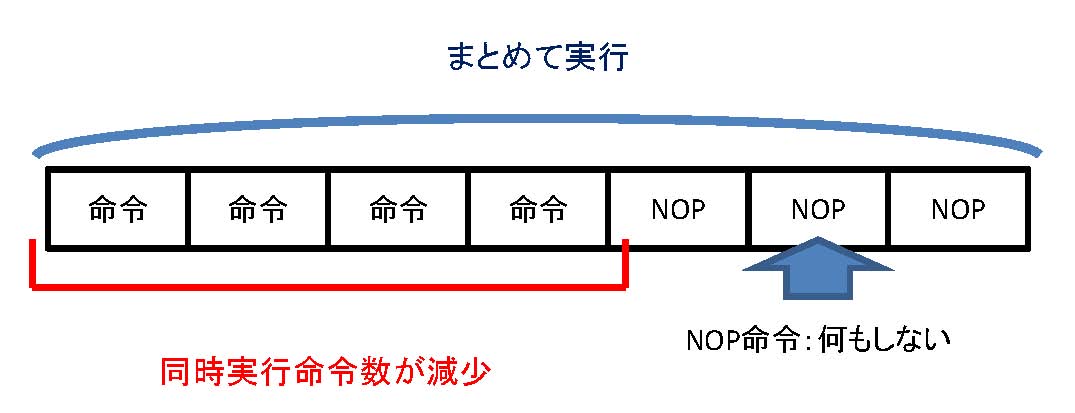

VLIWプロセッサの実行ユニットを有効に使いたい!

RISC 操作を並べ替えた結果、定められたVLIW 命令長に満たない場合には、NOP(何もしない) 命令を挿入し、命令語を構成する。このようなNOP 命令が多く存在すると、VLIW プロセッサの実行ユニットに割り当てる命令数が少なくなり、VLIW プロセッサの実行ユニット数に応じる単位時間に当たり処理能力、即ちスループットが低くなるという問題点がある。

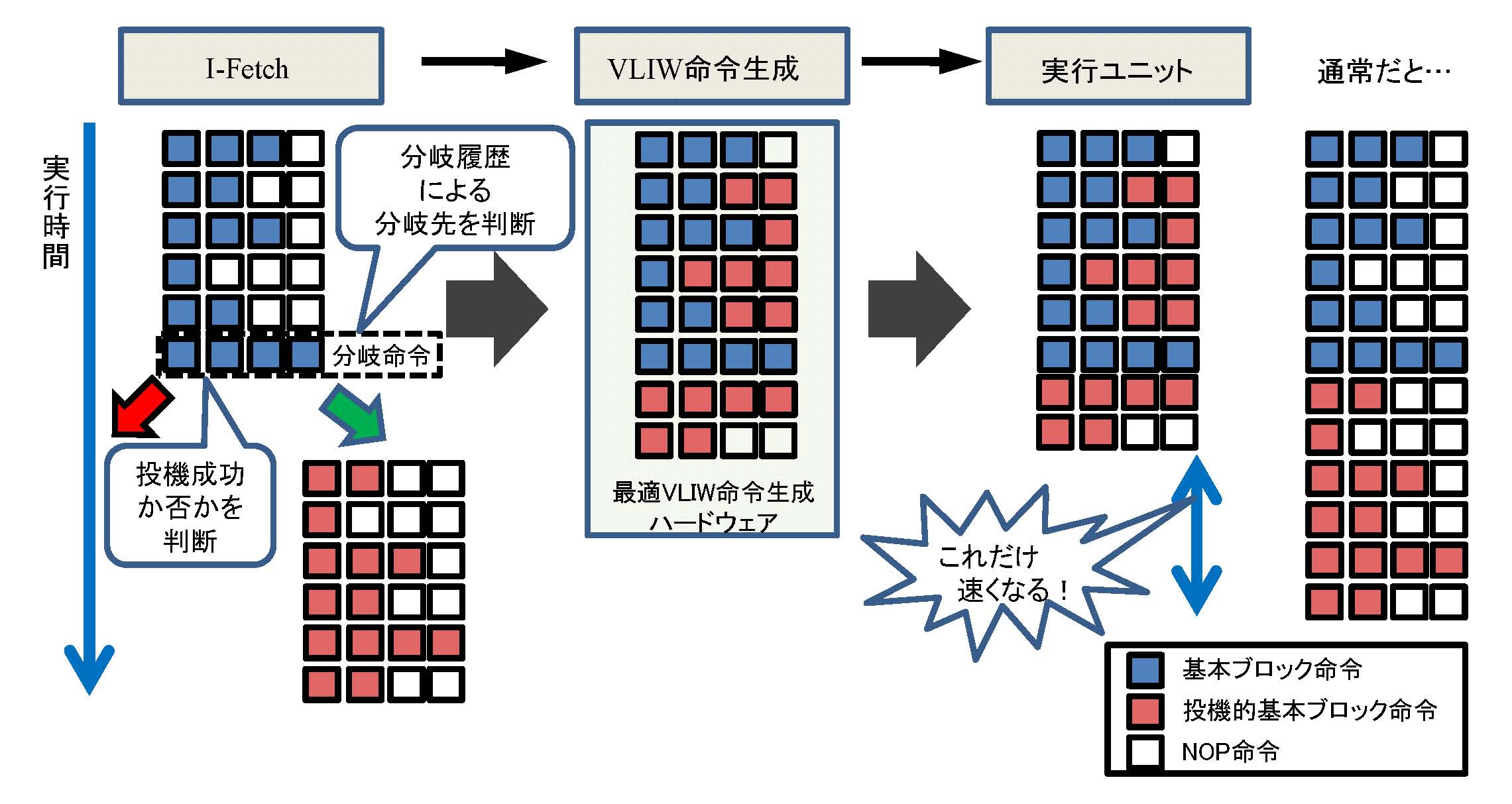

このような問題に対し、分岐履歴により条件分岐命令の分岐先にある基本ブロックを投機実行スレッドとし、当該条件分岐がある基本ブロックのNOP 命令を埋めて並列に実行する方法、すなわち、基本ブロックを投機の単位とする投機手法BBPC(Basic Block Parallel Computing)を提案する。

BBPC(Basic Block Parallel Computing)

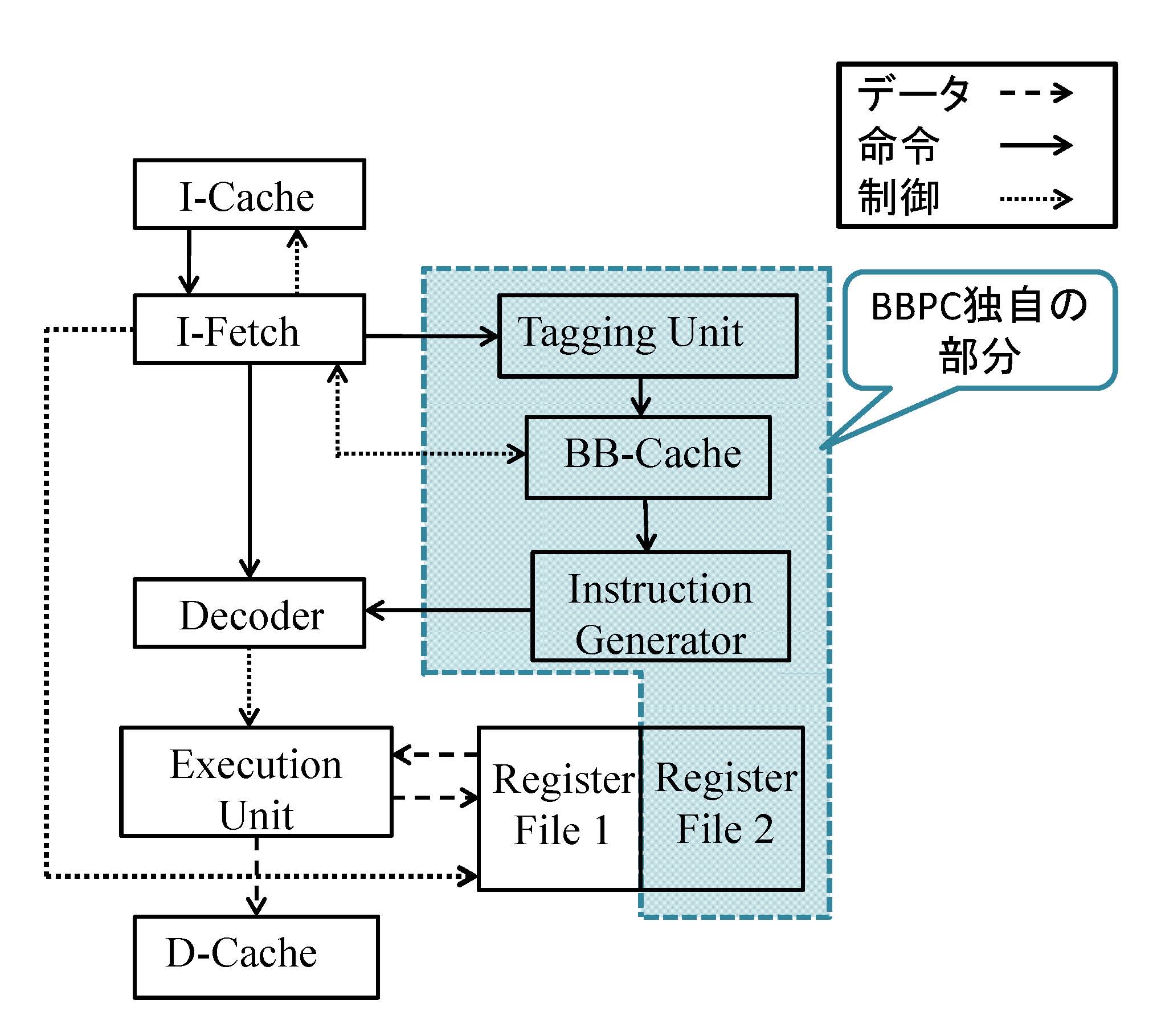

BBPCは一般のVLIWプロセッサをベースとして投機的実行を実現するためにBB-Cache、Tagging Unit、Instruction Generator、Register Fileを追加している。ハードウェアモジュールの設計、設計した回路の論理合成は完了している。

現在は、BBPCの有効性を評価するために、各機構を十分に機能検証し、ソフトウェアでのシミュレーション環境を構築しているところである。

- BB-Cache

ループの上位2パス命令を基本ブロック単位として保存する専用キャッシュメモリである。

- Taggig Unit

データ依存緩和手法を実現するモジュールの1つとして、BB-Cacheに保存していく各基本ブロック命令の目的レジスタ指定フィールドによりレジスタ番号と書き込み数に関する情報(IRFW情報)を収集する。

- Instruction Generator

Tagging Unitで生成したIRFW情報とBB-Cacheから受信した命令に基づいて最適化されたVLIW命令を生成する。

BBPCの原理

BBPCのアーキテクチャ構成