PALSプロジェクト

背景

現在普及しているプロセッサ(CPU)は複数のコアを持っている。その複数のコアを使いプログラムを並列実行することで、コアを1つしか使用しないで実行する場合に比べてプログラムの実行を早く完了できる。

それでは、どのようにプログラムを並列実行するか…様々な並列化手法の研究開発が行われている中、本研究室ではスレッドレベル並列性を抽出するアプローチとして2パス限定投機方式を提案している。

2パス限定投機方式とは?

2パス限定投機方式は、スレッドが実行されるプログラム上の経路(パス)を投機の対象とするパスベースの投機的マルチスレッド処理である。2パス限定投機方式で、スレッドの実行はプログラムにおいて実行頻度の高い(実行される回数が多い)ホットループのループ・イテレーション単位で行う。さらに、頻繁に実行されるパスを抽出し、そのうち実行頻度上位2つのパスに限定して投機実行を行う。

なんで、投機実行の対象を2つに限定するの?

プログラムのホットループの中で実行されるパスの実行頻度を調査したところ、実行頻度上位2つのパスの割合が全体のうち7〜8割以上であり、ほとんど実行が実行頻度上位2つのパスのいずれかで実行されることがわかった。よって、実行される確立が低いものよりも、実行される確立の高いものを予測した方が簡潔で予測もあたりやすいのではないかという考えのもと、投機対象を実行頻度上位2つのパスに限定している。

2パス限定投機システム PALS

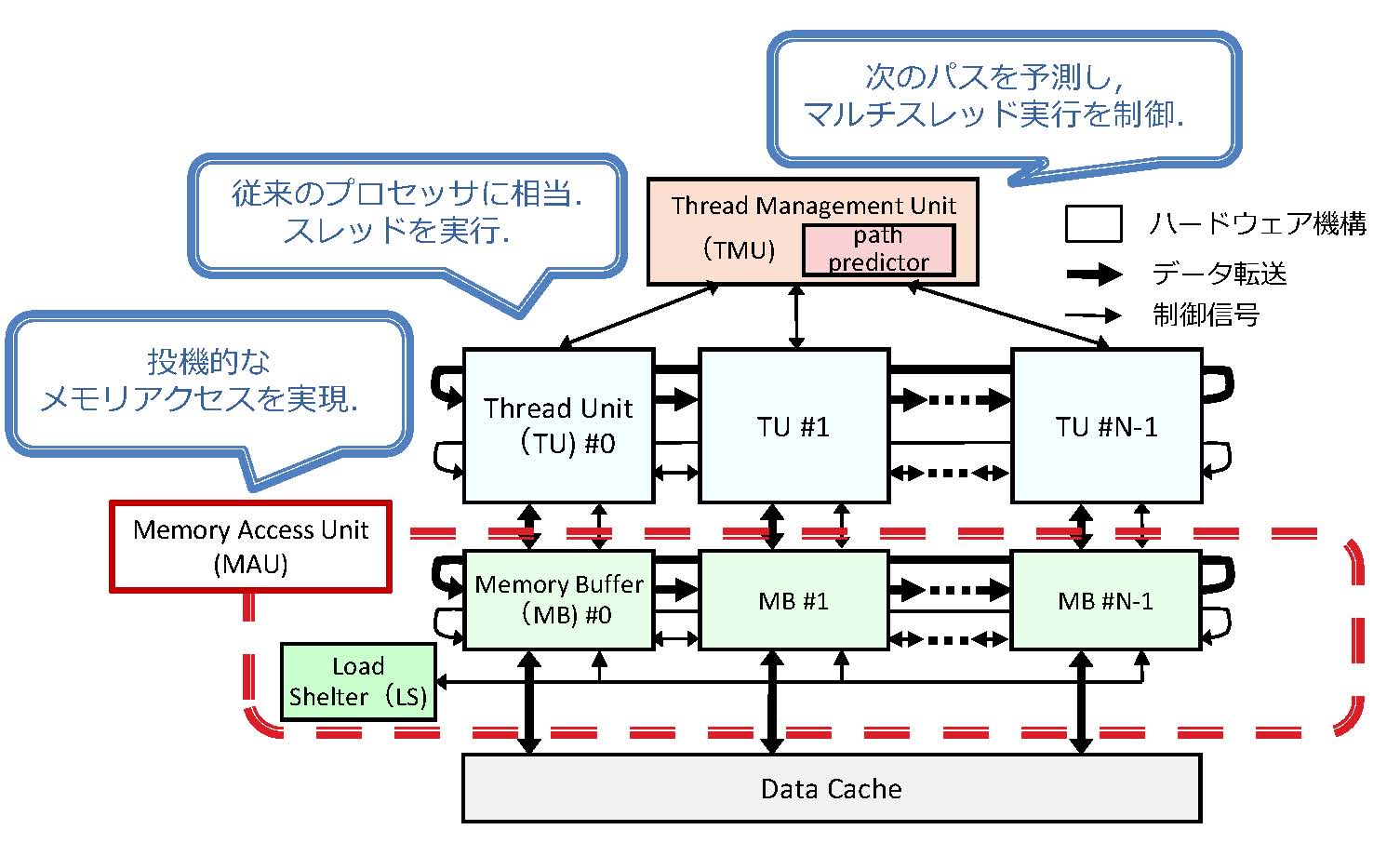

PALS(PAth Limited Speculation)は、2パス限定投機方式をクロックレベルで正確に模擬することを目的としたシミュレータである。PALSは次のようなハードウェア構成となる。

現在は、PALSのソフトウェアシミュレータpalsを用いて様々な研究を行っている.

- スレッド制御機構(Thread Management Unit:TMU)

各TUの動作状況を把握し、スレッドを投機的に起動するユニットである。内部に2レベルパス予測器を含む。

- スレッド処理機構(Thread Unit:TU)

計算を行うプロセッサコアである。

- 記憶機構(Memory Buffer:MB)

投機的なスレッドのメモリアクセスを適切に処理するための記憶装置である。

- 補助記憶機構(Load Shelter:LS)

MBの記憶容量を補助するための機構である。

- L1データキャッシュ(L1 Data Cache)

具体的な研究内容

- 最適投機対象パスの動的変更手法の検討

- 最適なパス予測機構の検討

- 投機スレッドコードの最適化

PALSのハードウェア構成